# CMSIS Standard and TivaWare Library

Prof. Hugo Vieira Neto 2020/1

## Objective

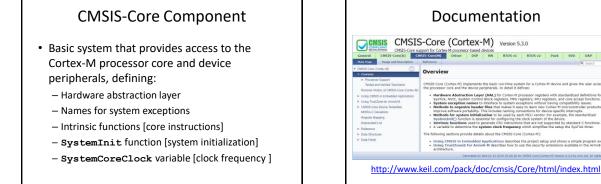

- To study the main features of the CMSIS standard and TivaWare library:

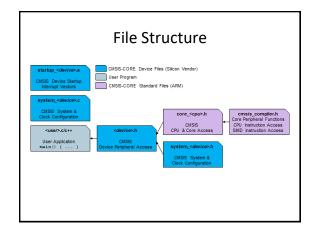

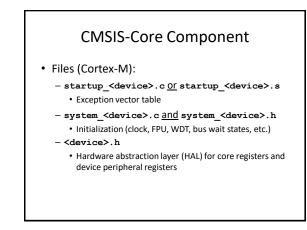

- CMSIS-Core

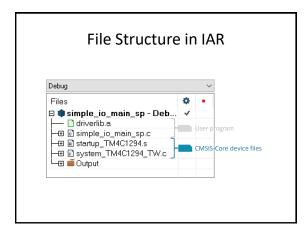

- Project file structure

- Standard system exception names

- Hardware abstraction layers

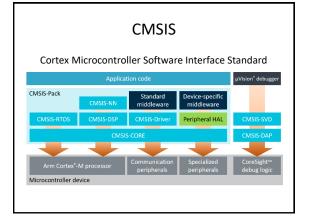

## Main Components

- CMSIS-Core

- API for Cortex-M or Cortex-A cores

- CMSIS-Driver

- Generic drivers for communication systems, file systems, graphic user interfaces, etc.

- CMSIS-DSP

- Digital signal processing library

- CMSIS-NN

- Neural network implementation library

- CMSIS-RTOS

- API for real-time operating systems

### 1

## System Exception Names

- Reset\_Handler

- NMI\_Handler

- HardFault\_Handler

- MemManage\_Handler

- BusFault\_Handler

- UsageFault\_Handler

- SVC\_Handler

- DebugMon\_Handler

- PendSV\_Handler

- SysTick\_Handler

## Hardware Abstraction Layer

- Data structures with pointers to registers in each device block

- Single header file (TM4C1294NCPDT.h)

- Example of use:

- GPIOK->DIR accesses the DIR register in block GPIOK (address 0x40061400)

- See Section 10.5 of the TM4C1294NCPDT device datasheet

## **Datasheet Information**

| GPIO Port A (AHB): 0x4005.8000                                   | Offset           | Name     | Туре |

|------------------------------------------------------------------|------------------|----------|------|

| GPIO Port B (AHB): 0x4005.9000<br>GPIO Port C (AHB): 0x4005.A000 | <del>0x000</del> | GPIODATA | RW   |

| PIO Port D (AHB): 0x4005.B000                                    | <b>0x400</b>     | GPIODIR  | RW   |

| GPIO Port E (AHB): 0x4005.C000<br>GPIO Port F (AHB): 0x4005.D000 | 0x404            | GPIOIS   | RW   |

| SPIO Port G (AHB): 0x4005.E000                                   | 0x408            | GPIOIBE  | RW   |

| PIO Port H (AHB): 0x4005.F000<br>PIO Port J (AHB): 0x4006.0000   | 0x40C            | GPIOIEV  | RW   |

| PIO Port K (AHB): 0x4006.1000 K                                  | 0x410            | GPIOIM   | RW   |

| GPIO Port L (AHB): 0x4006.2000<br>GPIO Port M (AHB): 0x4006.3000 | 0x414            | GPIORIS  | RO   |

| PIO Port N (AHB): 0x4006.4000                                    | 0x418            | GPIOMIS  | RO   |

| PIO Port P (AHB): 0x4006.5000<br>PIO Port Q (AHB): 0x4006.6000   | 0x41C            | GPIOICB  | W1C  |

## **TivaWare Library**

- Also provides an abstraction layer

- Macros for register access

- Multiple header files with the base addresses for each block and the offsets for each register (inc/hw\_\*.h)

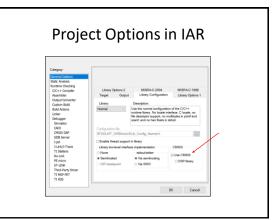

- Important: the target device for compilation must be defined (e.g. PART\_TM4C1294NCPDT)

- Options  $\rightarrow$  C/C++ Compiler  $\rightarrow$  Preprocessor

### TivaWare Library

- Example of access to a register:

HWREG (GPIO\_PORTK\_BASE + GPIO\_O\_DIR)

- The HWREG macro is defined in hw\_types.h

- GPIO\_PORTK\_BASE = 0x40061000 defined in hw\_memmap.h

- GPIO\_O\_DIR = 0x00000400 defined in hw\_gpio.h

## TivaWare Peripheral Driver Library

- Device driver API for device peripherals (driverlib/\*.h)

- Definitions of constants for configuration of peripherals

- - GPIO\_DIR\_MODE\_OUT = 0x00000001

- GPIO\_DIR\_MODE\_HW = 0x00000002

# Code Legibility

- Which of the equivalent code versions presented below is more legible?

- GPIOK->DIR |= GPIO\_PIN\_1

- GPIOK->DIR |= 0x0000002

- See "TivaWare Peripheral Driver Library User's Guide"

- GPIOPinTypeGPIOInput(GPIO\_PORTK\_BASE, GPIO\_PIN\_1)

- See inc/hw\_memmap.h e driverlib/gpio.h

### Exercise

- Select the "simple\_uart" project from the "EK-TM4C1294XL\_IAR" workspace.

- Use a terminal emulator application such as Tera Term with a serial connection to "COMn: Stellaris Virtual Serial Port" to communicate with the EK-TM4C1294XL kit.

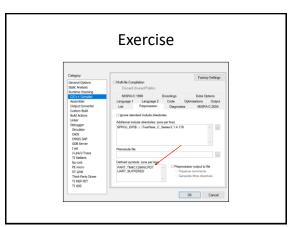

### Exercise

- Notice that the project makes use of the "uartstdio.c" file in "TivaWare\_C\_Series-2.1.4.178\utils"

- Macro PART\_TM4C1294NCPDT must be defined for proper configuration of RX and TX pins

- Macro UART\_BUFFERED must be defined if interrupt-controlled buffering is to be used

#### Exercise

- A quick look at the files "uartstdio.h" and "uartstdio.c" provides important information:

- UART\_RX\_BUFFER\_SIZE defines the receive buffer size, which can be overriden

- <code>UART\_TX\_BUFFER\_SIZE</code> defines the transmit buffer size , which can be overriden

- UARTStdioIntHandler is the UART interrupt handler name, which is different from the default in "startup\_TM4C1294.s"

### Exercise

- Inspect the "simple\_uart.c" file:

- What does the UARTInit function do?

- What happens if one removes the definition of PART\_TM4C1294NCPDT from the C/C++ Compiler Preprocessor options in IAR?

- How was the problem with the name of the UART interrupt handler having a name other than the default in "startup\_TM4C1294.s" handled? Are there alternative solutions? What are the potential problems with them?

### Exercise

- Make changes to the code so that the SysTick handler besides alternating the state of LED D1 also sends "SysTick\_Handler\n" via UART

- Observe what happens in Tera Term are the messages received synchronized with changes in the state of LED D1?

- <u>Note</u>: baud rate should be set to 9600 bps

### Exercise

- Pause the program in IAR and inspect these variables:

- -g\_ui32UARTTxWriteIndex

- -g\_ui32UARTTxReadIndex

- -g\_pcUARTTxBuffer

- What do these variables tell you? See comments for "output ring buffer" in "uartstdio.c"

- What happens if the baud rate is lowered to 600 bps? And to 300 bps? Do not forget to reset both sides of the connection (kit and Tera Term)